# Wafer Thinning for 3D Integration

Ricardo I. Fuentes Materials and Technologies, Corp. (MATECH) Wappingers Falls, NY, USA.

Abstract-We are fast approaching the limits of what can be achieved by shrinking IC groundrules. Moore's Law, which states that the number of transistors on an integrated circuit doubles approximately every two years, is no longer true. Transistor counts are expected to increase at a slower pace for the next few years, doubling only every three years or so. In light of this decreasing trend, the increase in functionality can be expected to come from a combination of transistor count and packing density-3D chip stacking or 3D packaging. Since the thinner the die, the more die can be stacked per unit volume, a common thread through virtually all modern packing processes is wafer thinning. We will discuss an all-chemical wafer thinning process (WaveEtch<sup>TM</sup>) that is inexpensive, single-sided, and that is compatible with wafer thickness of down to 40 µm, or less. The WaveEtch<sup>™</sup> process effectively decouples chemistry from transport phenomena, thus increasing uniformity and providing greater flexibility in working with novel chemistries. Aside from blanket thinning, it can also create unique final surface textures on scales of nanometers to micrometers. The tools' design allows for uniform etching of nearly any substrate type and material; from round to rectangular, for semiconductor, optical, and solar applications.

Keywords—Texturing, Chemical Thinning, Etching, Stress Relief, WaveEtch, Linear Scan.

### I. INTRODUCTION

Even though, in essence, wet etching is a simple process; i.e. the removal of material during the interaction between a liquid and a solid substrate, it can involve a series of complicated steps which combined effect leads to the resulting structure or surface. It remains popular in the semiconductor, solar, packaging, optoelectronic, as well as in many other industries because it is often the fastest and most cost-effective way to remove material [1] selectively or across an entire surface.

Thinner packages, higher power densities, and the ever increasing functionality of systems-in-a-pack (SiP) are driving the need for more robust, lower cost, higher yield thinning technologies [2]. While today, roughly 1/3 of all wafers are thinned [3], almost 3/4 of all wafers processed by 2017 are expected to be thinned [4]. Memory and logic comprise the largest fraction of thinned wafers, but power devices, backside illuminated sensors (BIS) CMOS imaging sensors (CIS), are strong drivers as well.

The strong demand for mobile devices is expected to remain steady thus maintaining the pressure on better, more cost effective thinning technologies. 3D TSV is hitting volume levels and 25  $\mu$ m memory stacks are around the corner. Even though insulatedgate bipolar transistors (IGBT) already use thin wafers, other power devices are adopting them as well [3]. Also, photovoltaic substrates make use of chemical thinning to reduce the thickness of the wafers as well as to texture the surface. Surface texturing is also critical in some IC metallization steps.

When the substrate can be wetted on both sides, immersion is a common choice for etching and chemical thinning. If the substrate can only be exposed to the chemicals on one side, spin or spray etching become reasonable candidates, but all these technologies have their shortcomings, such as radial and transport-induced non-uniformities [5]. Also, conventional technologies often result in undesirable exposure of the non-process side to residual liquid or vapors.

The need to alleviate the shortcomings of conventional etching technologies, as well as the increased power and flexibility that the control of some of the kinetic variables during etching brings to wet processing, make LinearScan etching a very exciting and powerful technology. Surface texturing is an excellent case in which the LinearScan added control yields engineered surfaces in a faster, more cost effective manner.

New device manufacturing techniques have become more demanding, which often requires the use of single-wafer, single-sided processing. In addition, thinner, denser packages, the push for increased functionality and decreased cost are driving this trend6.

## **II. LINEAR SCAN ETCHING**

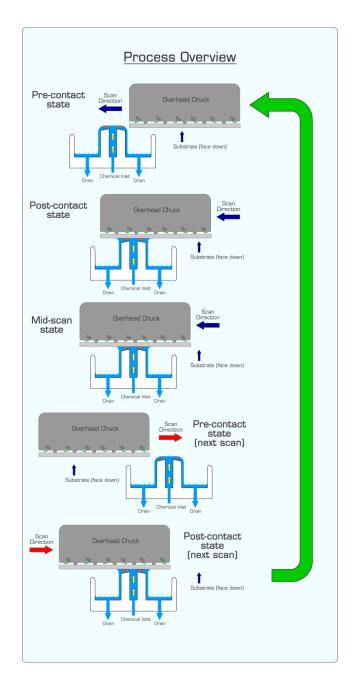

The WaveEtch<sup>TM</sup> LinearScan™ etching technology provides high uniformity as well as true single-sidedness on ultra-thin, large substrates [7,8]. It addresses the main shortcomings of conventional wet processing by providing a consistent and uniform supply of chemicals throughout the liquid-solid interface while making available an orthogonal path for the byproducts, such as gases and vapors. Exposure of every surface element to the same chemical and transport environment makes the process intrinsically uniform (Fig. 1). The solid-liquid interface (boundary layer) is not subject to speed gradients, convection, or other transport-related gradients that may cause variations in its thickness and its concomitant impact on uniformity. The system virtually all transport-related eliminates and centrosymmetrical non-uniformities, which plague spin/spray and immersion processes. Reactants enter the reaction zone through the bottom of the pool, while the byproducts exit in a plane parallel to the substrate surface; this delays solution saturation, extends bath life, and insures a consistent supply of fresh chemicals to the surface. The substrate is not immersed, but merely put in contact with the top of the pool's meniscus, as also illustrated in Fig. 1.

Most chemistries used with these processes do not require surfactants and are used in smaller volumes at lower flow rates, allowing for more efficient chemical usage [9].Together, these features lower chemical usage and its associated purchase and disposal costs, as well as often easing environmental regulatory compliance, resulting in overall production and costsof-ownership reduction.

LinearScan etching processes are size- and shapeindependent. Since all areas are exposed to the same chemical and transport environment, the size and shape of the substrate are largely irrelevant. A process developed for a given substrate geometry, can be readily used for another substrate geometry, thus making product process migration effortless and cost effective. These systems naturally accommodate odd, noncircular, thick shapes, and structures larger than 300mm.

## III. ORTOGONAL PATHS AND SURFACE EVOLUTION

LinearScan technology allows increased control over events that influence surface development which is crucial in the formation of textured or engineered surfaces. The separate, orthogonal paths that reactants and by-products (including gaseous byproducts) take during linear scan etching as well as the control over the time chemicals are in contact with the surface

Fig. 1. Schematic representation of the LinearScan process depicting the substrate material being removed by the etching process (held process side down), as well as the orthogonal paths of the reactants and the byproducts. The shaped flow of gas (DynamicConfinement), preventing the encroachment of fluid and vapors onto the non-process side (top), is also shown N2. Material removal (etching) occurs as the wafer is being gently scanned over a narrow pool of chemicals. Note the different paths the reaction byproducts take to avoid interference with the supply of fresh reactants to the reaction zone.

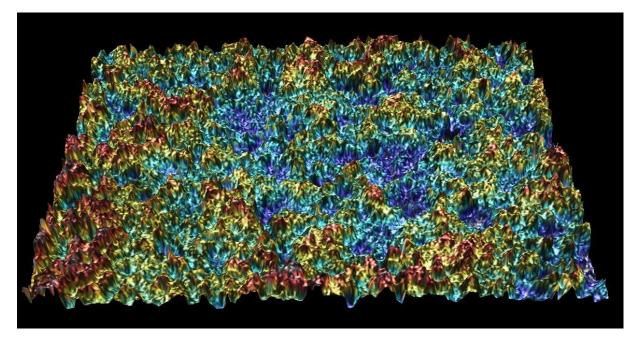

**Fig. 2.** Confocal microscope rendered image of a LinearScan textured surface with an acidic solution viewed at 50X magnification. Note the complex and convoluted nature of the surface, and the absence of smooth flat facets. Sa=0.65  $\mu$ m, Sq=0.81  $\mu$ m, Sz=7.52  $\mu$ m (average, RMS, and maximum roughness depth areal parameters respectively, as per ISO 25178). Such surfaces offer an increased surface area for mechanical interlocking of deposited films, as often required in backside metallization.

between scans, allow for a variety of surfaces to be engineered. Textured surfaces are required in applications such as solar cells and backside metallization to achieve lower reflectivity and improved adhesion, respectively.

Gas evolution during etching plays an important role in surface development, as well as "bubble" nucleation and detachment. LinearScan allows for control of some of the parameters that determine such bubble formation and the impact that the size and spatial distribution of their gas-solid interfaces has on the formation of the surface during etching. Parameters such as scan speed and surface fluid velocity determine the thickness of the boundary layer and the consequent transport characteristics of the process.

Acidic textures are oftentimes desirable because they are faster to achieve and produce complex nonfaceted surfaces. LinearScan produces acidic textures of a wide range of scales and on different materials. Fig. 2 shows the image of a silicon textured surface for a backside metallization application. The peak-tovalley scale is approximately 7  $\mu$ m although the attainable range by the LinearScan acidic texturing processes is from sub-micron to tens of microns. These surfaces are produced in a few seconds to a couple of minutes depending on the amount of material to be removed and the desired final roughness. It is important to notice the complex and non-faceted nature of the surfaces which is a desirable morphology for applications such as backside metallization. The convoluted nature of the surface allows for a very large interfacial area between the metal film and the substrate material resulting in considerable "interlocking" and consequentially increased adhesion strength. The technology is equally capable of producing faceted surfaces by alkaline processes [9].

### IV. THINNING AND PACKAGING

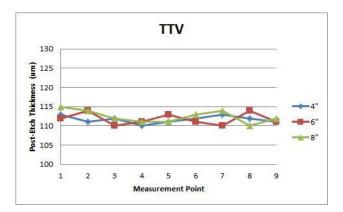

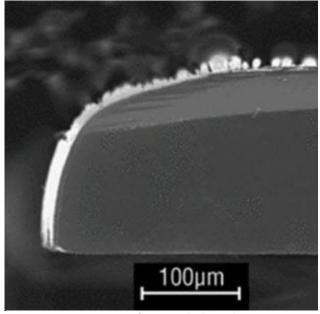

Wafer thinning is one of the native applications of the LinearScan etching technology. It allows for thinning of mounted or un-mounted, taped or un-taped substrates with superior uniformity (Fig. 3), no edge damage (Fig. 4), and without requiring any form of backside protection. Substrate assemblies, at any point in the packaging process, of virtually any thickness, structure, and size are all compatible with the LinearScan etching process. Chemical thinning is also an important step in removing sub-surface damage after grinding or other stress-inducing operations.

Fig. 3. WaveEtch technology is size independent as illustrated by TTV data on Si wafers 4", 6", and 8" in diameter.

Fig. 4. Cross section SEM of WaveEtch-thinned to 125 um Si wafer. Notice smooth edge and lack of rollover and edge serrations. The etch process does not require backside protection of any sort.

LinearScan etching systems are particularly well suited to handle and process very thin substrates. The unique process is carried out with no violent spinning, no need for lateral confinement by pins or other hard devices that may damage the wafer's edge, and no dynamic loading due to high rotational speeds. In the absence of hydrodynamic edge effects, the edges of the wafers are free of edge sharpness and the formation of other features common in spin/spray etch systems that significantly weaken the substrates [10]. The ability to use virtually any chemistry to interact with any substrate material enables the systems to process any material of interest. In addition to packaging applications, the systems are being used to etch or thin InP, Ge, GaAs, Si, polysilicon, glass, and quartz, among others. Substrates of odd shapes and within a large range of size and thickness are being processed. This method provides a new way to do wet thinning for packaging applications in a more precise, efficient, and environmentally friendly manner.

#### ACKNOWLEDGEMENTS

WaveEtch<sup>™</sup>, LinearScan<sup>™</sup>, and DynamicConfinement<sup>™</sup> are trademarks of Materials and Technologies Corp. (MATECH)

Ricardo I. Fuentes is the founder and president of Materials and Technologies, Corp., (MATECH), 22 Bill Horton Way, Wappingers Falls, NY 12590, United States. Phone (845) 463-2799, e-mail info@matech.com.

### REFERENCES

- Marc J. Madou, "Fundamentals of microfabrication: the science of miniaturization" 2002 CRC Press, LLC, p. 110.

- [2] Robert Castellano, "Wafer & Device Packaging and Interconnect" September/October 2010 p.10.

- [3] Eric Mounier and Amandine Pinagalli, "Thin wafers win majority in electronics by 2016," Solid State Technology, October 2011.

- [4] Yole Development Report, Thin Wafers, Temporary Bonding Equipment & Materials Market 2012, October 2012.

- [5] Ricardo I. Fuentes, "Intrinsically Uniform Single-sided Wafer Thinning", Levitronix User Conference, 2011.

- [6] IWLPC, 6th Annual International Wafer-Level Packaging Conference proceedings, October 27-30, 2009, Santa Clara, CA.

- [7] Ricardo I. Fuentes, "Extending Process Flexibility for Singlewafer Etch," Solid State Technology, July 2007.

- [8] Ricardo I. Fuentes, "Single-sided Wafer Thinning and Handling," Chip Scale Review, Jan/Feb 2011.

- [9] Ricardo I. Fuentes, "Single-sided Wafer Thinning for 3D Integration," Annual International Wafer-Level Packaging Conference proceedings, 2010, Santa Clara, CA.

[10] G. Coletti, C.J.J. Tool and L. J. Geerligs, "MECHANICAL STRENGTH OF SILICON WAFERS AND ITS MODELLING," 15th Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Vail Colorado, USA, 7-10 August, 2005.