# ChipScaleReview.com ChipSc

The International Magazine for the Semiconductor Packaging Industry

January-February 2011

Volume 15, Number 1

- HDI for Flip Chip

- Copper Bond Test Challenges

- Relating Spring Probes to Signal Integrity

- Single Sided Wafer Thinning and Handling

- International Directory of Test & Burn-In Socket Suppliers

# Single Sided Wafer Thinning and Handling

By Ricardo I. Fuentes, Ph.D. [Materials and Technologies, Corp. (MATECH)]

any excellent articles have been written on conventional grinding, polishing, and thinning techniques; as well as on the many methods for bonding a wafer to a carrier for handling, thinning or processing. This article focuses on something different — a novel chemical technology that thins wafers down to 50µm or less, with better uniformity, and at a lower cost than conventional thinning. Additionally, it will also discuss methods of handling thin wafers without carriers of any sort, thus dealing with the inherent issues of wafer distortion, warpage, and extreme fragility.

Wafer thinning can be performed in several ways: 1) by grinding the wafer down (usually to 100 to 150 $\mu$ m), 2) by chemical mechanical polishing, which can bring the wafer thickness down to 50 $\mu$ m or less, 3) by chemical etching, which thins the wafer down and removes the subsurface damage left by grinding and polishing, and 4) by plasma etching. Usually a combination of grinding and one of the other methods is the most practical route to a cost effective thin die solution.

Most thin wafer handling is performed by bonding the wafer to a temporary carrier and thus handling the wafer in much the same way as a conventional thicker wafer. There are, however, applications where, for reasons of yield, economics, process flow, or device performance, it is preferable to handle the wafer without a carrier. It is this latter case that will be addressed here.

## **Thinning and Stress Relief**

Chemical thinning is a necessary step to eliminate the subsurface damage and relieve the stress that grinding and polishing leave behind. Chemical thinning is also an alternative to polishing (following grinding) as the method to make ultrathin wafers. It has the added benefit of completely eliminating damage or surface features that result in electrically active sites that other technologies may leave behind, which are deleterious to device performance.<sup>1</sup>

Wet etching involves the interaction between a liquid and a solid substrate and it is often the fastest, most cost-effective way to remove material<sup>2</sup> selectively or across an entire surface, as required in packaging applications and many other steps of semiconductor fabrication.

The demand for denser, lower package heights, higher power requirements, tighter total thickness variation (TTV) specs, and the development of higher-functionality systems-in-a-package (SiP) or systems-ina-foil (SiF) are driving the need for more robust, lower cost, higher yield thinning technologies with no end in sight.<sup>3,4,5</sup>

When the substrate may be wetted on both sides, immersion is a common choice for etching and thinning. If the substrate may only be exposed to etchants on one side, spin or spray become reasonable candidates, but each has its shortcomings \_ such as radial and transport-induced non-uniformities. Depending on the particular package or device requirements, improved uniformity (in terms of TTV) is often an important consideration; conventional technologies have clear limitations in terms of how much material they can remove while staying within the allowed TTV requirements. These technologies often result in undesirable exposure of the nonprocess side to residual liquid or vapors. This is of particular importance on freestanding wafers.

A novel etching technology\*, provides high uniformity as well as true singlesidedness on large ultrathin substrates. It addresses the main shortcomings of conventional wet processing by providing a consistent and uniform supply of chemicals throughout the liquid-solid interface while making available an orthogonal path for the byproducts, such as gases and vapors. Exposure of every surface element to the same chemical and transport environment makes the process

Figure 1. Schematic representation of the LinearScan process depicting the substrate material being removed by the etching process (held process side down), as well as the orthogonal paths of the reactants and the byproducts. The shaped flow of gas (DynamicConfinement), preventing the encroachment of fluid and vapors onto the non-process side (top), is also shown. Note the removal of material (etching) after the wafer has passed over the fluid meniscus and the different paths the reaction byproducts take to avoid interference with the supply of fresh reactants to the reaction zone. The top view illustrates the wafer being scanned repeatedly in alternating directions, as necessary, over the fluid meniscus showing the narrow reaction zone where thinning is in progress (wafer is being etched from below).

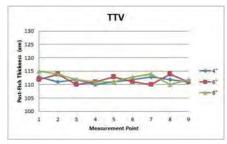

intrinsically uniform (**Figure 1**). The solid-liquid interface (boundary layer) is not subject to speed gradients, convection, or other transport-related gradients that may cause variations in its thickness and result in a large TTV. The system eliminates virtually all transport-related and centrosymmetrical non-uniformities that plague spin/spray and immersion processes. **Figure 2** shows the uniformity of 4", 6" and 8" wafers (as TTV) after the removal of 75µm with this proprietary tool. Substrates are held on their non-process side by a side-gripping or

Figure 2. The material removal uniformity (Total Thickness Variation or TTV) typical of the WaveEtch LinearScan thinning process is illustrated above. TTV ranges from  $\pm$  1.5µm for 4" wafers to  $\pm$  2.5 for 8" wafers after the removal of 75µm to reach a final thickness, in this case of 112µm.

Figure 3. Image of MATECH's side-contact chuck (CAT chuck). Notice the position of the fingers that have moved out of the way to avoid contact with the etching fluid while the remaining fingers stay in contact with the sides of the thin wafer keeping it within capture range of the fluid pool. The adaptive handling allows the chuck to manage ultrathin, severely distorted w afers while making no contact with the non-process side.

"caterpillar" non-contact chuck (or CAT chuck for its resemblance to the side motion of the namesake insect's legs), while being gently scanned over a narrow pool of etching chemicals. This novel chuck holds the ultrathin wafer by its edge and its legs retract sequentially out of the way as the wafer is scanned over the fluid meniscus, making no contact with the backside (non-process side) of the wafer, while still protecting it from vapor or liquid encroachment (**Figure 3**).

The reactants enter the reaction zone through the bottom of the pool, while the byproducts exit in a plane parallel to the substrate surface; this delays bath saturation, extends bath life, and ensures a consistent supply of fresh chemicals to the surface. The substrate is not immersed, but merely put in contact with the top of the pool's meniscus, as is also illustrated in **Figure 1**.

Chemicals and vapors are kept away from the non-process side by a proprietary gas sealing technology\*\* (Figure 1), which forms a gaseous O-ring around the periphery of the substrate to prevent any liquid or vapor incursion. In this way, the non-process side is not subject to physical or chemical contact, thus eliminating the need for any kind of backside protection, such as resist or tape.

Wafer thinning and stress relief are native applications of this etching technology. Additionally, substrate assemblies — at any point in the packaging process, and of virtually any thickness, structure, and size — are all compatible with the process.

The final thickness for modern IC device substrates continues to decrease, with 50µm being the current state-of-theart target for many modern devices.6 Linear scan etching systems are particularly well suited to handle and process very thin substrates. The unique process is carried out with no violent spinning, no need for lateral confinement by pins or other hard devices that may damage the wafer's edge, and no dynamic loading due to high rotational speeds. In the absence of hydrodynamic edge effects, the edges of the wafers are free of sharpness and the formation of "teeth", or other features common in spin/spray etch systems that significantly weaken the substrates.<sup>7</sup>

The chemistries used in linear scan systems do not require surfactants and are used in smaller volumes at lower flow rates, allowing for more efficient chemical usage. Chemicals can be used to a processdictated end-point without regard to surfactant depletion. Together, these features lower chemical usage and its associated purchase and disposal costs, as well as often easing environmental regulatory compliance resulting in overall production and costsof-ownership reduction. Chemical usage reduction can range from approximately 20% to a factor of two or more, depending on the process, method, and tooling used to perform it.

Since all areas are exposed to the same chemical and transport environment, the size and shape of the substrate are largely irrelevant. A process developed for a given substrate geometry can be readily used for other substrate geometries, making product process migration effortless and cost effective. linear scan etching systems naturally accommodate odd, noncircular, thick substrates, and structures larger than 300mm, as well as severely distorted wafers (up to 10 mm off-plane distortion). For cleaning applications, such as those sometimes required for 3D stacks' low standoff height structures or to remove residual polymer, the chemical process and the rinse steps may be augmented by the application of megasonics. Megasonics alter the behavior of the boundary layer, promote transport to reach crevices in complex or high aspect ratio structures,<sup>8</sup> and speed up the process and rinse steps. The interfacial control allowed by this technology enables unprecedented manipulation of the liquid-solid interface.

Since there is no mechanical contact with the surface of the substrate, linear scan systems are well suited for thinning and stress relief after grinding operations for packaging applications of very thin wafers. The process offers superior uniformity (Figure 2) and thus the ability to tune grinding operations for optimum yield, picking up more chemical removal if necessary, while staying within the TTV budget and lowering the cost of the whole operation. The systems can handle the single-sided wet etching of ultrathin wafers ( $\leq$  50µm) avoiding the risk of punch through due to their uniformity. Intrinsic limits of grinding operations and downstream yield losses (from de-taping or debonding) usually prevent grinding to thicknesses below 150 µm. The gentle and uniform nature of linear scan wet processing can easily thin well below 50µm.

## **Ultra-thin Wafer Handling**

Processes such as temporary bonding, back-grinding, metallization, etching, debonding, and dicing, all may involve some form of thin wafer handling. In general, all of these are carried out by bonding the device wafer to a temporary handle or carrier. The purpose of this operation is to handle the wafer throughout the process as a SEMI standard wafer would be handled, thus allowing use of existing equipment and facilities. To remove adhesive residue (usually by a wet process) and during packaging, the ultrathin wafers have to be detached from their carrier and handled freestanding. It is at this point that issues of breakage (i.e. yield) arise.

In these cases, thin wafers (as thin as  $50\mu m$ ) have to be handled directly. Among the common wafer handling technologies — vacuum chucking, gripping, and

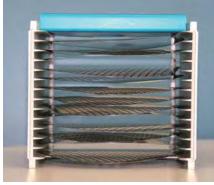

Figure 4. Image showing the large amount of out-ofplane distortion and warpage typical of unsupported ultrathin wafers. In this case approximately 10mm. Notice also the wide slots in the special cassette designed to accommodate said distortion.

Bernoulli — the latter is most suitable for ultrathin wafer handling between the cassette and the process station. The system is rugged, reliable and capable of a throughput of over 200wph.

There are two primary challenges in handling ultrathin wafers: distortion and breakage. The deflection of a wafer, in the absence of added stress, is proportional to the square of its radius and inversely proportional to the third power of its thickness. **Figure 4** shows the amount of distortion common in back end of the line (BEOL) freestanding ultrathin wafers. In this case, the distortion is approximately 10mm, compounded by the stress caused by additional layers deposited on them. Any method that will effectively hold and handle them must take this into account.

An end effector\*\*\* specifically designed to handle thin, distorted wafers was used (Figure 5). To planarize the wafer and confine its lateral motion, the end effector has a rim of very small fluoropolymer vacuum pads which make contact in the exclusion zone. This approach to lateral confinement is preferred to other contact methods which may chip or damage the edge of the wafer, resulting in reduced strength or breakage.

Figure 5. Bernoulli end effector effectively and consistently handles unsupported ultrathin wafers, down to 50μm thick. This image shows an 8" end effector used in conjunction with a WaveEtch system equipped with a side-contact CAT chuck. The etching system handles and processes freestanding 6" and 8" ultrathin wafers.

To assist in accommodating the extreme distortion, it is common for the cassette slots to be double-spaced as compared to standard wafer cassettes (**Figure 4**). Since the wafers can take a shape that is changing and unpredictable, the loaded cassette must be scanned before any wafer is moved out of it on into it. The cassette scanner measures the position of the edges

(continued on Page 53)

### CEA-Leti Ramps up 300mm Line Dedicated to 3D-Integration

Grenoble-based research institute, CEA-Leti, officially ramped one of Europe's first 300mm lines dedicated to 3D-integration applications in a ceremony on January 18, 2011. By adding this technology to its existing 300mm CMOS R&D line, Leti now can offer heterogeneous integration technologies to customers on both 200mm and 300mm wafers.

The new line, dedicated to R&D and prototyping, includes 3D-oriented lithography, deep etching, dielectric deposition, metallization, wet etching and packaging tools that will be available for Leti's customers and partners around the world. It will allow Leti to apply its 3D-integration generic processes on 300mm wafers.

"This extension offers important new capabilities to equipment manufacturers and other Leti partners," said Laurent Malier, CEO of Leti. "Together we will demonstrate 3D and heterogeneous integration technologies on 300mm wafers."

Laurent Malier and Susumu Kaminaga, President of SPP and chairman of SPTS. Mr Kaminaga gave Laurent Malier a present to thank him for their collaboration on the 300mm Line.

### (continued from Page 41)

of each wafer and provides the data for the wafer handling robot end effector.

Similarly, the aligner, which has a Bernoulli movable chuck, makes no contact with the wafer surface. To prevent the wafers from shifting positions after alignment, the aligner chuck and the end effector perform a "handshake" whereas the vacuum hold from the chuck is not released until the hold from the end effector is in place.

### Conclusion

The combination of Bernoulli and CAT non-contact chucks along with linear scan wet etching makes an excellent combination for wet processing and handling ultrathin freestanding wafers. The ability to use virtually any chemistry to interact with any substrate material enables the systems to process most materials of interest, all while retaining the ability to handle ultrathin wafers with severe warpage or distortion. In addition to packaging applications, the systems are being used to etch or thin InP, Ge, GaAs, Si, polysilicon, glass, and quartz, among others. Substrates of odd shapes and within a large range of size and thickness can also be processed. These methods provide a new way to wet thin and handle ultrathin wafers in a more precise, efficient, and environmentally friendly manner.

### **Acknowledgements**

\*WaveEtch<sup>TM</sup>, LinearScan<sup>TM</sup>, CAT<sup>TM</sup> Chuck and \*\*DynamicConfinement<sup>TM</sup> are trademarks of Materials and Technologies Corp. (MATECH) \*\*\*Mechatronic Bernoulli End Effector Ricardo Fuentes is the founder and president of Materials and Technologies Corp., (MATECH), 641 Sheafe Road, Poughkeepsie, NY 12601, United States; phone (845) 463-2799, e-mail *info@matech.com*. The author is thankful to Mechatronic Systemtechnik GmbH, Tiroler Strasse 80, 9500 Villach, Austria, for kindly providing some of the images in this paper.

### References

1. M. Reiche and G. Wagner, "*Wafer Thinning: Techniques for Ultra-thin Wafers*" Advanced Packaging, 2003, 3/1 2. Marc J. Madou, "*Fundamentals of microfabrication: the science of miniaturization*" 2002 CRC Press, LLC, p. 110.

3. Robert Castellano, "*Wafer & Device Packaging and Interconnect*" September/

October 2010 p.10. 4. IWLPC, 6<sup>th</sup> Annual International Wafer-Level Packaging Conference proceedings, October 27-30, 2009. Santa Clara, CA. 5. Burghartz, J.N. Harendt, C. Tu Hoang Kiss, A. Zimmermann, *"Ultra-thin chip* fabrication for nextgeneration silicon processes" Ripolar/ **RiCMOS** Circuits and Technology Meeting, 2009. BCTM 2009.

IEEE, 12-14 Oct. 2009, p. 131 - 137 6. Dustin Warren, Bioh Kim, Thorsten Matthias, Markus Wimplinger and Paul Lindner, "Advanced Temporary and Permanent Bonding Technology" IWLPC, 6<sup>th</sup> Annual International Wafer-Level Packaging Conference proceedings, October 27-30, 2009, Santa Clara, CA. 7. G. Coletti, C.J.J. Tool and L. J. Geerligs, "Mechanical Strength of Silicon Wafers and its Modelling" 15<sup>th</sup> Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes, Vail Colorado, USA, 7-10 August, 2005.

8. Chantal Khan Malek and Sasi Yajamanyam, "Evaluation of alternative development process for high-aspectratio poly (methylmethacrylate) microstructures in deep x-ray lithography," J. Vac. Sci. Technol. B 18, p. 3354 (2000).